搜索结果: 61-75 共查到“集成电路技术 芯片”相关记录100条 . 查询时间(0.188 秒)

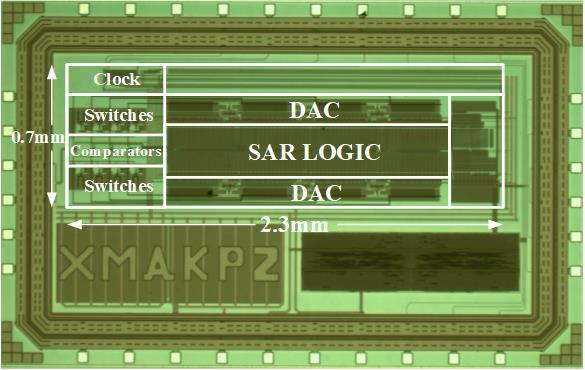

近日,科睿唯安(Clarivate Analytics)公布了基本科学指标(ESI)数据库最新数据,西安电子科技大学杨银堂、朱樟明教授团队在集成电路领域国际期刊《IEEE Trans. on Circuits and Systems I: Regular Papers》发表的论文《A Reconfigurable 10-to-12-b 80-to-20-MS/s Bandwidth Scalabl...

2018年9月12-13日,第二届“清华-麻省理工-斯坦福-伯克利”未来芯片技术研讨会在清华大学举办。围绕集成电路三维技术这一主题,来自清华大学、麻省理工学院、斯坦福大学、加州大学伯克利分校四所高校的学者与泛林集团、西部数据等产业界人士,共同探讨集成电路三维技术发展趋势,分享最新研究成果。本次研讨会由清华大学未来芯片技术高精尖创新中心与泛林集团联合主办。

全新方法能“看清”微芯片设计

计算机芯片 微芯片 三维图像

2017/3/16

英国《自然》杂志2017年3月14日发表的一篇纳米科学论文,展示了“详观”微芯片的全新方法――一种可生成高分辨率集成电路(计算机芯片)三维图像的技术,而在试验中,研究人员事先并不知道所涉及的集成电路的设计。该成果将为医疗和航空领域的关键芯片生产带来革新。

电子科技大学成都学院集成电路原理课件第十二章 芯片工程与多项目晶圆MPW加工服务。

德国参与欧盟研究项目加强下一代高性能芯片研发

德国 欧盟 高性能芯片

2015/8/7

德国联邦教研部和欧盟委员会相关负责人于近日共同启动了欧洲研究项目“七纳米技术”(SeNaTe)。该项目旨在开发更小、更紧凑的集成电路,从而大幅度提高芯片的计算能力。来自科学界和工业界的42个欧洲伙伴共同合作,将集成电路的结构尺寸缩小到目前最好芯片尺寸的一半。

半导体集成电路芯片质量与可靠性保证方法

半导体集成电路芯片 质量 可靠性

2016/9/21

针对国内目前没有专门用于保证半导体集成电路芯片质量与可靠性要求的相关标准,相应测试、可靠性 研究水平也较为落后的情况,对半导体集成电路芯片质量与可靠性保证方法进行研究。介绍半导体集成电路芯片质 量与可靠性保证方面的国际、国内标准与技术水平现状,提出在目前技术水平下需从设计、工艺、筛选验证3 个方 面保证半导体集成电路芯片质量与可靠性,在筛选验证方面提出芯片筛选、封装样品考核相结合的方式。结果表明,...

中国密码学会2012年密码芯片学术会议在清华大学召开(图)

TCG密码芯片 高速密码专用芯片 低功耗密码电路

2012/9/25

由中国密码学会密码芯片专业委员会主办、清华大学微电子学研究所承办的“中国密码学会2012年密码芯片学术会议”于8月26─28日在北京清华大学FIT楼多功能报告厅举行。来自国内高等院校、科研院所、检测机构及商用密码企业等集成电路设计行业专家学者、研究人员、技术开发人员和在读研究生180余人参加了会议。会议开幕式由中国密码学会密码芯片专委会副主任委员、清华大学微电子学研究所白国强副教授主持。清华大学微...

中国科学院微电子研究所研制成功8GS/s 4bit ADC和10GS/s 8bit DAC芯片(图)

8GS/s 4bit ADC 10GS/s 8bit DAC芯片 微波器件 集成电路

2012/5/11

近日,微电子所微波器件与集成电路研究室(四室)超高速电路课题组在超高速ADC/DAC芯片研制上取得突破性进展,成功研制出8GS/s 4bit ADC和10GS/s 8bit DAC芯片。ADC芯片采用带插值平均的Flash结构,集成约1250只晶体管,测试结果表明芯片可以在8GHz时钟频率下稳定工作,最高采样频率可达9GHz。超高速DAC芯片采用基于R-2R的电流开关结构,同时集成了10Gbps自...

电子封装正朝着高密度封装的方向发展,以满足市场对高性能、高可靠性、低成本、微型化的电子产品的需求.高密度封装具有多学科交叉的特点.综述课题组多年来在芯片高密度封装互连技术,包括倒装芯片(flip chip,FC)凸点制备/转移技术、导电胶高密度互连技术、叠层芯片封装技术及封装可靠性方面的研究工作,并指出未来高密度封装技术的发展方向.

作为一种能够在微米级尺度操纵液体的新兴技术, 微流控芯片已经受到科学家们的广泛关注. 高密度集成的微流控芯片装置可以实现高通量并行化的实验以及多种操作单元的功能一体化, 作为一种新的方法学平台, 已经越来越多地应用于化学和生命科学的研究中. 本文着重介绍了集成化微流控芯片装置的基本概念、构建方法、及其在细胞生物学、分子生物学以及化学合成应用研究中的最新进展, 尤其强调了集成微流控芯片系统在传统方法...

一种用于电容型体硅微陀螺的低噪声读出电路芯片

微陀螺 读出电路 低噪声

2010/1/18

读出电路位于微传感器系统信号通路的最前端,是决定系统性能的关键因素。本文针对音叉式体硅微陀螺的具体应用,提出了一种低噪声电容读出电路,芯片采用斩波技术降低了电路的低频1/f噪声、失调电压以及参考电压失配的影响,提高了读出电路的分辨率和动态范围;提出一种噪声电荷转移的分析方法,用于分析和预测读出电路的噪声性能;建立一种简化的微陀螺传感器仿真模型,用于模拟读出电路对微传感器的响应。读出电路在0.35 ...

高精度可编程恒流驱动白光LED芯片设计研究

运算放大器 LED 恒流驱动

2009/10/21

实现了一种高精度可控白光LED恒流驱动芯片的设计.使用自动调零技术在内部集成了自动调零运算放大器,并采用外接电阻和使能设计控制恒定LED驱动电流,可在2.9 V到4.4 V的工作电压范围内提供3个不同的恒定驱动电流,最大驱动电流可达1 A.测试结果表明,当驱动电流从200 mA变化到800 mA时,外接电阻电流和LED驱动电流之比变化小于2.3%; 电源电压跳变±10%的情况下,800 mA的驱动...

针对传统的基于纯硬件平台的FPGA芯片测试方法所存在的种种问题,提出并验证了一种基于软硬件协同技术的FPGA芯片测试方法。该方法引入了软件的灵活性与可观测性等软件技术优势,具有存储深度大、可测I/O管脚数目多、自动完成配置下载(不需人工干预)和自动定位FPGA中的错误等优点,提高了FPGA的测试速度和可靠性,并降低了测试成本,与传统的自动测试仪(ATE)相比有较高的性价比。采用软硬件协同方式针对X...

离散子波分解的专用芯片设计及CPLD实现

离散子波变换 滤波器组 下二采样

2009/4/27

子波变换是信号处理和图像压缩等诸多领域中一个非常有效的数学分析工具。日前,其实现方式多为软件编程。本文针对子波变换与滤波器组的关系,在卷积滤波、下二采样过程中,将数据按一定规律重排,用复杂可编程逻辑器件(CPLD)设计了一种专用芯片(ASIC)可完成离散子波分解,具有一定的实用价值。