搜索结果: 1-15 共查到“电子科学与技术 Chip”相关记录23条 . 查询时间(0.078 秒)

A new chip for decoding data transmissions demonstrates record-breaking energy efficiency(图)

数据传输 新芯片 能源效率

2023/6/8

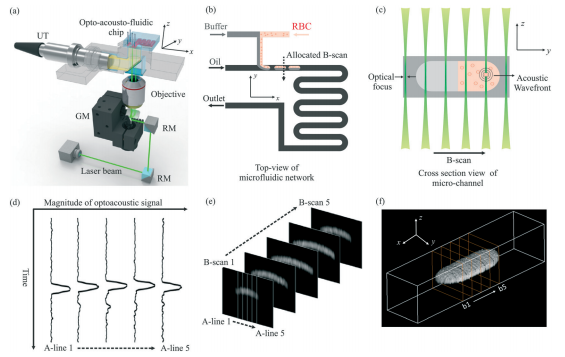

中国地质大学科学技术发展院宋潮龙等机电学院, Lab on a Chip, 27 March 2018. Opto-acousto-fluidic microscopy for three-dimensional label-free detection of droplets and cells in microchannels(图)

荧光剂;纳米颗粒;实现;物质;检测;分析

2021/10/21

2018年3月27日,微流控领域国际顶级期刊《Lab on a Chip》刊发了中国地质大学机电学院宋潮龙教授的最新研究成果:“Opto-acousto-fluidic microscopy for three-dimensional label-free detection of droplets and cells in microchannels”,该论文被推荐为封面文章。

Placement and Routing For A Field Programmable Multi-Chip Module

Placement Routing Field Programmable Multi-Chip Module

2015/8/14

Placement and Routing For A Field Programmable Multi-Chip Module.

On-Chip True Random Number Generation in Nanometer CMOS

True Random Number Generation Process Variation Circuit calibration

2014/12/8

On-chip True Random Number Generator (TRNG) forms an integral part of a number of cryptographic systems in multi-core processors, communication networks and RFID. TRNG provides random keys, device id ...

半导体研究所视觉芯片(Vision Chip)研究取得新的进展

视觉芯片 研究

2011/11/7

视觉芯片是一种由图像传感器阵列和阵列型并行信息处理器构成的半导体集成化片上系统芯片。它克服了现有视觉图像系统中的串行数据传输和串行信息处理速度限制瓶颈,可以在片上实现最高速度达到每秒一千帧以上的高速图像获取和智能化视觉信息处理,在高速运动目标的实时追踪、机器视觉、虚拟现实、快速图像识别、智能交通及各类智能化玩具等领域具有广泛的应用前景。

视觉芯片是一种由图像传感器阵列和阵列型并行信息处理器构成的半导体集成化片上系统芯片。它克服了现有视觉图像系统中的串行数据传输和串行信息处理速度限制瓶颈,可以在片上实现最高速度达到每秒一千帧以上的高速图像获取和智能化视觉信息处理,在高速运动目标的实时追踪、机器视觉、虚拟现实、快速图像识别、智能交通及各类智能化玩具等领域具有广泛的应用前景。

ASU scientists improve chip memory by stacking cells

ASU scientists chip memory stacking cells

2009/12/23

Scientists at Arizona State University have developed an elegant method for significantly improving the memory capacity of electronic chips.Led by Michael Kozicki, an ASU electrical engineering profes...

Hybrid automatic repeat request (HARQ) is used in high-speed uplink packet access (HSUPA) to increase the data rate. Chase combining is the simplest of HARQ algorithms. It provides a time diversity an...

Fast and Efficient On-Chip Interconnection Modeling for High Speed VLSI Systems

IC design RC/RLC Interconnection VLSI Systems

2010/2/2

Timing driven physical design, synthesis, and

optimization tools need efficient closed-form delay models for

estimating the delay associated with each net in an integrated circuit

(IC) design. The ...

Passive On-Chip Components for Fully Integrated Silicon RF VCOs

Passive On-Chip Components Integrated Silicon RF VCOs

2010/12/7

In this work integrated passive devices used in RF VCOs are presented. The operation of on-chip inductors and variable capacitors is outlined along with simple electrical equivalent circuits suitable ...

Simulation of Crosstalk in High-Speed Multi-Chip Modules

Crosstalk High-Speed Multi-Chip Modules

2010/12/14

Simulation results of the electrical performance at 1 GBits/sec of a number of different off-chip interconnection architectures are presented with emphasis given to the dependence of crosstalk and sig...

Humidity Effect on Chip Capacitors With Al2O3 Multistage Anodised Films

Chip capacitors aluminum oxide capacitors humidity effects

2010/12/16

In this paper the properties of capacitors with porous-barrier and barrier-type Al2O3 layers under humidity tests are described and compared. The capacitance, conductance and dissipation factor of the...